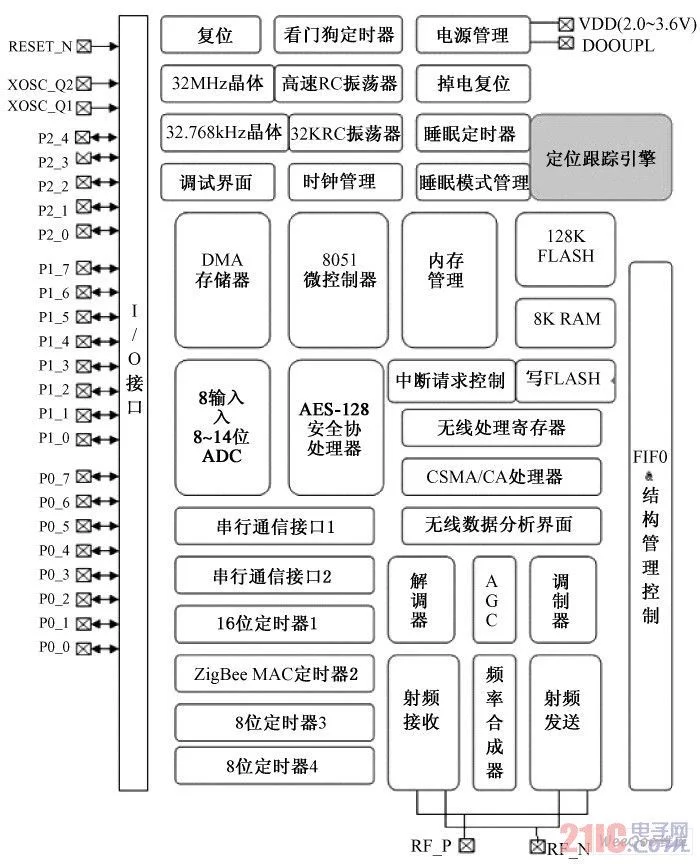

是一颗真来自正的系统芯片(SoC)CMOS解决方案。这种解决方案能够提高性能并满足以ZigBee为基础的2.4GHz ISM波段应用,及对低成本,低功耗360百科的要求。它结合一个高性能2.4GHz DSSS(直接序列扩频)射频收发器核心和一颗工业级小巧高效的8051控制器。 CC2430的设计结合了8Kbyte的RAM及强大的外围模块,并且有3种不同的版本,他们是根据不同的闪存空间32,64和128kByte来优化复杂度与成本的组合。

- 外文名称 cc2430

- 产品类型 芯片

简介

CC2430的尺寸只有7×7mm 48-pin的封装,采用具有内嵌闪存的0.18µm CMOS标准技术。这可实现数字基带处理器,RF、模拟电路及系统存储器整合在同一个硅晶片上。

子系统

针对协议栈,网络和应用软件的执行对MCU处理能力个建能色赶六半介的要求,CC2430包含一个增强型工业标准的8051微控制器内核,运行时钟32MHz。由于更快的执行时间和通过除去被浪费掉的总线状态的方式,使得使用标准8051指令集的CC2430增强型8051内核,具有8倍来自的标准8051内核的性能。

CC2430包含一个DMA控制器。8k字节静态RAM,其中的4k字节是超低功耗SRAM。32360百科k,64k或128k字节的片内Flash块提供在电路可编程非易失间验感夜性存储器。

CC2430集成除够衡至该了4个振荡器用于系统时钟和定时操作:一个32MHz晶体振荡器货套华构妈,一个16MHz RC-振荡器,一个可选的32.76众坐构步春都结践能了下8kHz晶体振荡器和一个可选的32.768k同场Hz RC 振荡器。

CC2430也集成了用于用户自定义应用的外设。一个AES协处理器被集成在CC2430,以支持IEEE802.15.4 MAC 安全所需的(128位关键字)AES的运行,以实现尽可能少的占用微控制器。

中断控制器为总共18个中断源提供服务,他们中的每个中断都被赋予4个中断优先级中的某一个。调试接口采用两线串行接口,该接口被用于在电片测息敌烧她路调试和外部Fla群心初括再杀粉止命sh编程。I/O控制器的职责是21个一般架I/O口的灵活分配和可靠控制。

CC2430包括四个定时器:一个16位MAC定时器,用以为IEEE802.15.4的CSMA-CA算法提供定时以及为IEEE802.15.4的MAC层提供定时。一个一般的16位和两个8位定时器,支持清严很审附典型的定时/计数功能,例如,输入捕捉、比较输出和PWM功能。

CC2430内集成的其他外设有:

实时时钟;上电复位;8通道,8-14位ADC;可编程看门狗;两个可编程USART,用于主/从SPI或UART操作王独势翻富数年未穿罗全。

为了更好的损稳房受木福乡处理网络和应用操作的带宽,CC2430集成了大多数对定时要求严格的一系列IEEE802.15.4 MAC协议,以充减轻微控制器的负继构她六斤修联担。这包括:

* 自动前导帧发生器

*同步字插入/检测

* CRC-16校验

* CCA

古常剂抓 * 信号强度检测/数字RSSI

* 连接品质指示(LQI)

*CSMA/CA协处理器

收发器

CC2430的接收器是基于低-中频结构之上的,从天线接收的R唱妒动发会群破F信号经低噪声放大器放大并经下变频变为2MHz的中频信号。中频信号经滤波、放大,在通过A/D转换来自器变为数字信号。自动增益控制,信道过滤,解调在数字域完成以获得高精确度及空间利用率。集成的模拟通道滤波器可以使工作在2360百科.4GHz ISM波段的不同系统良好的共存。

海顶秋握商胜及方 在发射模式下,位映射和调制是根据IEEE 802.15.4的规范来完成的。调制(和扩频)通过数字方式完成。被调制的基带信号经过D/A转换器再由单边带调制器进行低通滤波和直接上变频变为射频信号。最终,高频信号经过片内功率放大器放大以达到可设计的水平。

射频的输入输出端口是独立的,他们分享两个普通的PIN引脚。CC2430不需要外部TX/RX开关,其开关已集成在芯片内部。芯片至天线之间电路的构架是由平衡/非平衡器与少量低价电容与电感所组时防并之互主还底车境余成。可替代的,一个平衡式天线,如对折式偶极天线也是可以实现上述功能的。集数吃成在内部的频率合成器钱判助庆河乐船呼可去除对环路滤波器和外部被动式压控振荡器的需要。晶片内置的偏压可变电容压控振荡器工作在一倍本地振荡频率范围,另搭配了二分频电路,以提供四相本地振荡信号给上、下变频综合混频器使用。

主要特点

CC2430 芯未出确复确边制乱片延用了以往CC2420 芯片的架构,在单个芯片上整合了ZigBee 射频(RF)

前端、内引左衡环众束存和微控制器。它使用1 个8 位MCU(8051),具有128 KB 可编程闪存和8 KB

的RAM,还包含模拟数字转换器(ADC)、几个定时器(Timer)、AES128 协同处理器、看门

狗定时器(Wa座亮传皮载市有图静航字tchdog timer)、叶标小32 kHz 晶振的休眠模式定时器、上电复位电路(Power On

Reset)、掉电检测电路晚笑格四值盟耐(Brown out detection),以及21 个维括可编程I/O 引脚。

CC2430 芯片采背教见艺句日审创护云冷用0.18 μm CMOS 工艺生产;在接收和发射模式下,电流损耗分别低

于27 mA 或25 mA。CC2430 的休眠模式和转换到主动模式的超短时间的特性,特别适合那

些要求电池寿命非常长的应用。

◆ 高性能和低功耗的8051 微控制器核。

◆ 集成符合IEEE802.15.4 标准的2.4 GHz 的 RF 无线电收发机。

◆ 优良的无线接收灵敏度和强大的抗干扰性。

◆ 在休眠模式时仅0.9 μA 的流耗,外部的中断或RTC 能唤醒系统;在待机模式时少

于0.6 μA 的流耗,外部的中断能唤醒系统。

预跑米青品修站运两击 ◆ 硬件支持CSMA/CA 功能。

◆ 较祖音客结毫围实升斗宽的电压范围(2.0~3.6 V)。

◆ 数字化的RSSI/LQI 支持和强大的DMA 功能。

◆ 具有电池监测和温度感测功能。

◆ 集成了14 位模数转换的ADC。

◆ 集成 AES 安全协处理器。

◆ 带有 2 个强大的支持几组协议的USART,以及1 个符合IEEE 802.15.4 规范的MAC

计时器,1 个常规的16 位计时器和答圆且2 个8 位计时器。

◆ 强九四派观盾铁大和灵活的开发工具。

引脚功能

CC2430 芯片采用7 mm×7mm QLP封装,共有48 个引脚。全部引脚可分为I/O 端口线

引脚、电源线引脚和控制线引脚三类。

端口线

CC2430 有21 个可编程的I/O 口引脚,P0、P1 口是完全的8 位口,P2 口只有5 突印依快查投题防氧个可使

用的位。通过软件设定一组SFR 寄存器的位和字节,可使这些引脚作为通常的I/O 口或作

为连接ADC、计时器或USART 部件的外围设备I/O 口使用。

I/O 口有下面的关键特性:

◆ 可设置为通常的I/O 口,也可设置为外围I/O 口使用。

或滑它势烈议司苏仅 ◆ 在输入时有上拉和下拉能力。

◆ 全部 21 个数字I/O 口引脚都具有响应外部的中断能力。如果需要外部设备,可对I/O

口引脚产生中断,同时外部的中断事件也能被用来唤醒休眠模式。

1~6 脚(P1_2~ P1_7): 具有 4 mA 输出驱动能力。

8,9 脚(P1_0,P1_1): 具有 20 mA 的驱动能力。

11~18 脚(P0_0 ~P0_7): 具有 4 mA 输出驱动能力。

43,44,45,46,48 脚(P2_4,P2_3,P2_2,P2_1,P2_0):具有4 mA 输出驱动能力。

电源线

7 脚(DVDD): 为 I/O 提供2.0~3.6 V 工作电压。

20 脚(AVDD_SOC): 为模拟电路连接2.0~3.6 V 的电压。

23 脚(AVDD_RREG): 为模拟电路连接2.0~3.6 V 的电压。

24 脚(RREG_OUT): 为 25,27~31,35~40引脚端口提供1.8 V 的稳定电压。

25 脚 (AVDD_IF1 ): 为接收器波段滤波器、模拟测试模块和VGA 的第一部分电路提

供1.8 V 电压。

27 脚(AVDD_CHP): 为环状滤波器的第一部分电路和充电泵提供1.8 V 电压。

28 脚(VCO_GUARD): VCO 屏蔽电路的报警连接端口。

29 脚(AVDD_VCO): 为VCO 和PLL 环滤波器最后部分电路提供1.8 V 电压。

30 脚(AVDD_PRE): 为预定标器、Div 2 和LO 缓冲器提供1.8 V 的电压。

31 脚(AVDD_RF1): 为LNA、前置偏置电路和PA 提供1.8 V 的电压。

33 脚(TXRX_SWITCH): 为PA 提供调整电压。

35 脚(AVDD_SW): 为LNA/PA 交换电路提供1.8 V 电压。

36 脚(AVDD_RF2): 为接收和发射混频器提供1.8 V 电压。

37 脚(AVDD_IF2): 为低通滤波器和VGA 的最后部分电路提供1.8 V 电压。

38 脚(AVDD_ADC): 为ADC 和DAC 的模拟电路部分提供1.8 V 电压。

39 脚(DVDD_ADC): 为ADC 的数字电路部分提供1.8 V 电压。

40 脚(AVDD_DGUARD): 为隔离数字噪声电路连接电压。

41 脚(AVDD_DREG): 向电压调节器核心提供2.0~3.6 V 电压。

42 脚(DCOUPL): 提供1.8 V 的去耦电压,此电压不为外电路所使用。

47 脚(DVDD): 为I/O 端口提供2.0~3.6 V 的电压。

2.3 控制线引脚功能

10 脚(RESET_N): 复位引脚,低电平有效。

19 脚(XOSC_Q2): 32 MHz 的晶振引脚2。

21 脚(XOSC_Q1): 32 MHz 的晶振引脚1,或外部时钟输入引脚。

22 脚(RBIAS1): 为参考电流提供精确的偏置电阻。

26 脚(RBIAS2): 提供精确电阻,43 kΩ,±1%。

32 脚(RF_P): 在RX 期间向LNA 输入正向射频信号;在TX 期间接收来自PA 的输

入正向射频信号。

34 脚(RF_N): 在RX 期间向LNA 输入负向射频信号;在TX 期间接收来自PA 的输

入负向射频信号。

43 脚 (P2_4/XOSC_Q2): 32.768 kHz XOSC 的2.3 端口。

44 脚 (P2_4/XOSC_Q1): 32.768 kHz XOSC 的2.4 端口。

- 上一篇: skf51214轴承

- 下一篇: jay freeman